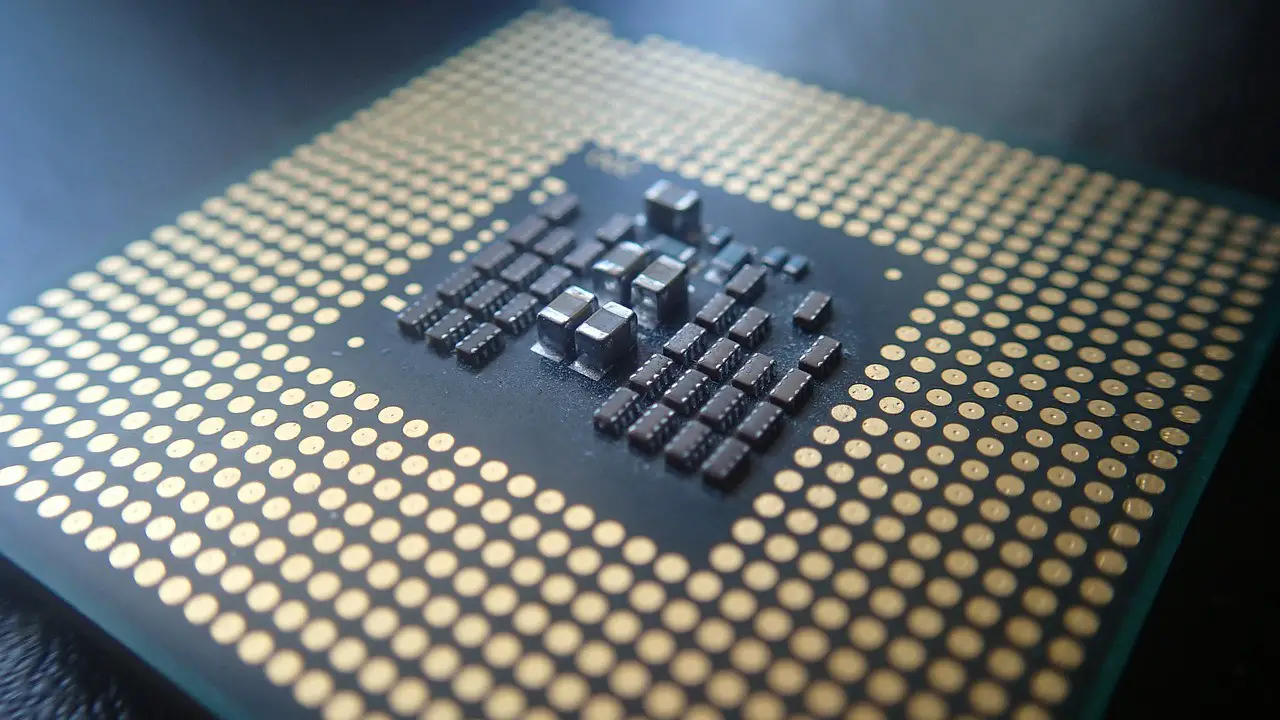

主要半导体制造商的供应商公司 ASML 预测,到 2030 年将生产 1nm 处理器。英特尔、台积电和三星等半导体制造商正在使用先进的光刻技术来减小晶体管的尺寸,因为他们设法缩小的每一纳米都是巨大的一步。

1nm 处理器将在 2030 年准备就绪

目前,3nm 晶体管已经在生产中,但荷兰公司 ASML 宣布了其计划在未来几年内制造第一批 1nm 以下晶体管。 但是,英特尔首席执行官 Pat Gelsinger 已经表示,业界应该停止讨论纳米,而应该开始讨论埃 (Å)。 埃是一个长度单位,通常在指波长和分子距离时使用,相当于 0.1 纳米。

已经在测试纳米以下的新技术

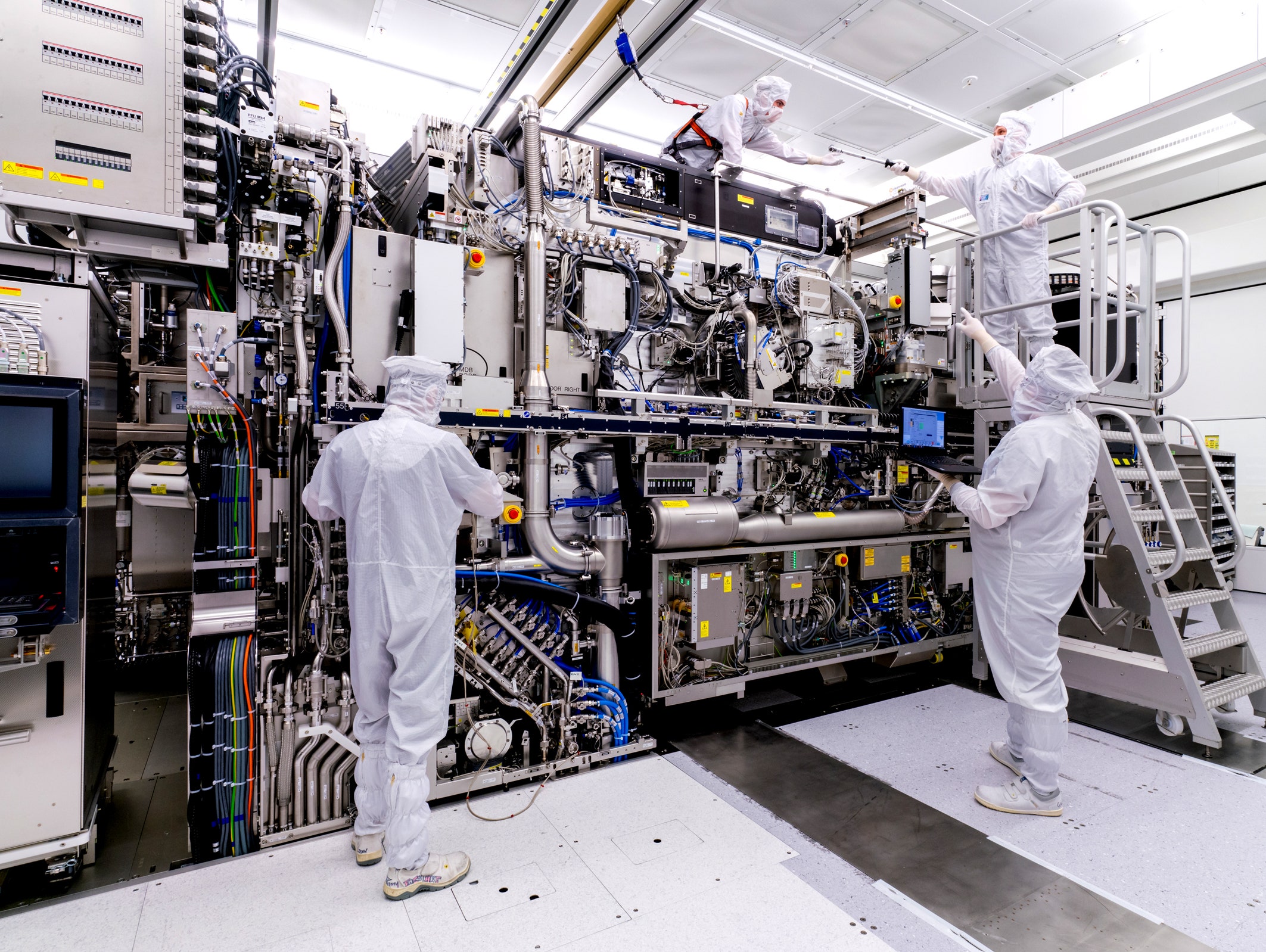

在其投资者活动中,ASML 详细介绍了其战略中最相关的要点,并提供了许多有关未来十年半导体制造工艺的细节。 据该公司称,在未来几年内,我们将看到向 High-NA(高数值孔径)技术的飞跃。

这是一个包含采用全新设计的光学器件的平台,可以将当前极端光刻平台的分辨率提高多达 70%。 这是一台精度更高的机器,将用于 3nm 及以下制造工艺。 到 2030 年,ASML 预计将晶体管尺寸减小到纳米以下。 到 2026 年,我们将达到 1.4 纳米(或 14 埃),到 2030 年,我们预计将达到 0.7 纳米(或 7 埃)。

这种小型晶体管不会使用三星等制造商使用的 FinFET 技术制造。 相反,必须应用诸如 2D 原子通道或互补 FET 等技术,这些技术包括垂直堆叠晶体管。 到 2030 年,这家荷兰公司的主要客户之一台积电计划制造具有超过 3000 亿个晶体管的处理器。 相比之下,NVIDIA Ampere GPU 拥有 540 亿个晶体管,而基于 Zen 2 的 AMD Epyc Rome CPU 已经采用 7nm 工艺制造,拥有 390 亿个晶体管。

半导体危机结束?

ASML 估计半导体制造的效率将继续提高,每两年效率增长约 3 倍,直到 2040 年。预测是乐观的,ASML 预计其极紫外 (EUV) 光刻机到 2025 年将准备就绪 95%,扩大日产能提高50%以上。 换句话说,半导体生产背后的大公司不仅预计半导体危机会结束,而且产量将翻番。